最新文章

赛灵思低功耗 FPGA与Algotronix MACsec内核

Algotronix采取了不同寻常的措施,即为所有许可的内核提供HDL源码。这样做的主要动机是支持客户检查,以便确保代码不含病毒或特洛伊木马代码,而且不会强制进入非授权状态或操作。有了源码,就能降低客户安全审核的成本和复杂性。此外,源码可加速设计进程,因为工程师能够方便地尝试使用诸如加密、解密或加密/解密等不同配置参数和密钥长度,并了解其各自仿真内核中的信号状态。

数据中心内部通信可根据需要进行组织来分隔选定的机架,进而提供虚拟隔离区。这种功能可保护数据完整性,并应对数据中心和云应用中的隔离问题。无论是意外错误连接还是恶意行为(见图4),MACsec系统都能检测到未经认证的数据包,系统管理员可通过设置策略将其隔离或删除。

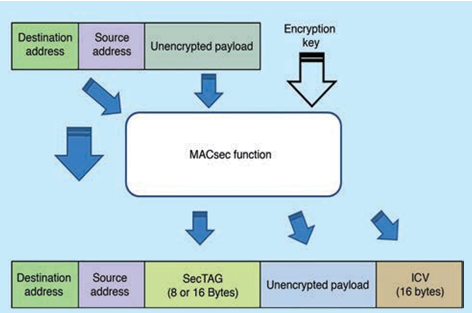

图3 – MACsec帧结构包括MAC安全标签(SecTAG)字段,其可定义EtherType,并标明数据包是否加密。

图4 – MACsec将拒绝通过错误连接抵达的数据包,无论是因为意外情况造成还是恶意行为导致。

所有数据加密和解密都在端口级进行。除了附加的MACsec报头和较少的额外时延,打开端口级加密不会增加开支,也不会对性能造成其它影响。

通过采用符合IEEE 802.1AE要求的加密Ethernet Lecel 2方案,设备厂商现在能用这些内核推动其系统特色化。基于云的用户可能与其他用户相互之间不信任,但他们现在设备制造商则能选择可用的IP核来满足1Gb和10 Gb以太网吞吐量的需求。

能够从MACsec提供的数据机密大获裨益,并且数据源认证功能可进一步保护他们的数据。

您可对内核进行配置,通过实现较宽的数据路径来提高吞吐量,或通过选择较窄的数据宽度来最大程度地减小FPGA封装尺寸。拥有源码还有其它更多优势,包括更便于了解内核工作情况;也让文档记录和归档变得更快捷方便。

此外,还配套提供了广泛的验证测试平台,可帮助客户在ModelSim等工具中确认操作是否正确。测试平台包括MACsec的行为模型和MACsec IP核的自检版本,能针对行为模型检查可综合硬件的输出。这种自检设计可在用户仿真中实现实例化,便于测试实际用户设计环境下的内核表现,并在错误驱动的情况下提供有用的诊断信息。

内核可提供许多选项,因此精确的资源数量将取决于您如何选择参数,如数据速率、密钥长度和所选SecY数量以及其它。然而,赛灵思网站IP部分列出的10G MACsec内核采用6,638个slice、20,916个LUT和53个BRAM块。如需获取许可证选项,敬请联系Algotronix。

赛灵思低功耗 FPGA与Algotronix MACsec内核的完美结合为设备制造商实现产品差异化提供了高性能、低时延的解决方案。安全特性使得数据中心能够确保其客户机密,同时还可帮助安全管理员检测并打击恶意行为。